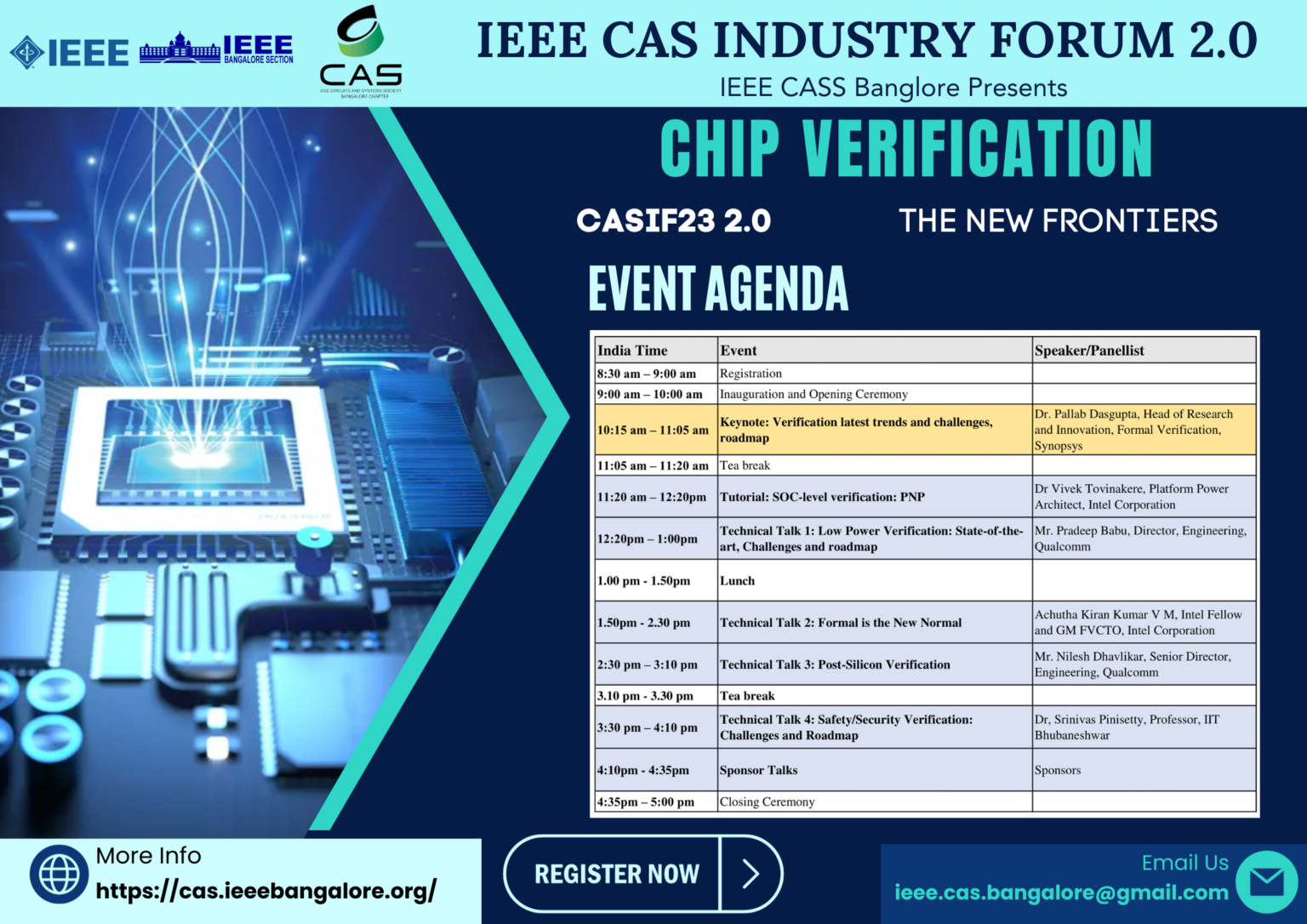

INDUSTRY FORUM 2.0

Join the IEEE CAS Bangalore Chapter for the “Chip Verification – The New Frontiers” Industry Forum. In today’s intricate chip design landscape, verification and validation have taken center stage, with verification costs comprising 70% of design budgets. This event brings together industry and academia experts to explore the latest advancements in chip verification, featuring enlightening keynotes, insightful tutorials, cutting-edge technical talks, and valuable networking opportunities. Gain profound insights from design automation (EDA) companies, semiconductor manufacturers, HPC specialists, and academia. Whether you attend in person or virtually, don’t miss this opportunity to be part of the future of chip verification.

Date: 18th November 2023

Time: 9:00 AM – 5:00 PM

Venue: Hilton Banglore Embassy Golf Links, Intermediate Ring Road

Event Mode: Hybrid

CHIEF GUESTS

Mr. Achutha Kiran Kumar V M

Intel Fellow and GM FVCTO, Intel

Dr. Prasant Misra;

Vice - Chair Industry Engagement

Dr. Chengappa

M R

Secretary

Subind Kumar;

Corporate VP, India Site

Head, Western Digital

Raj S Mitra;

VP at Cisma Consultants

SPEAKERS

Dr. Pallab Dasgupta

Research and Innovation on Formal Verification at Synopsys, Sunnyvale

Mr. Achutha Kiran Kumar V M

Intel Fellow and GM FVCTO, Intel

Mr. Nilesh Dhavlikar

SVE (SOC validation & Emulation) team, Qualcomm

Dr. Srinivas Pinisetty

Faculty (Computer Science and Engineering), SES, IIT Bhubaneswar

Dr. Vivek Tovinakere

Platform Power Architect (FPGAs) Programmable Solutions Group of Intel

Mr. Pradeep Babu

SOC Design Verification and Validation, Qualcomm

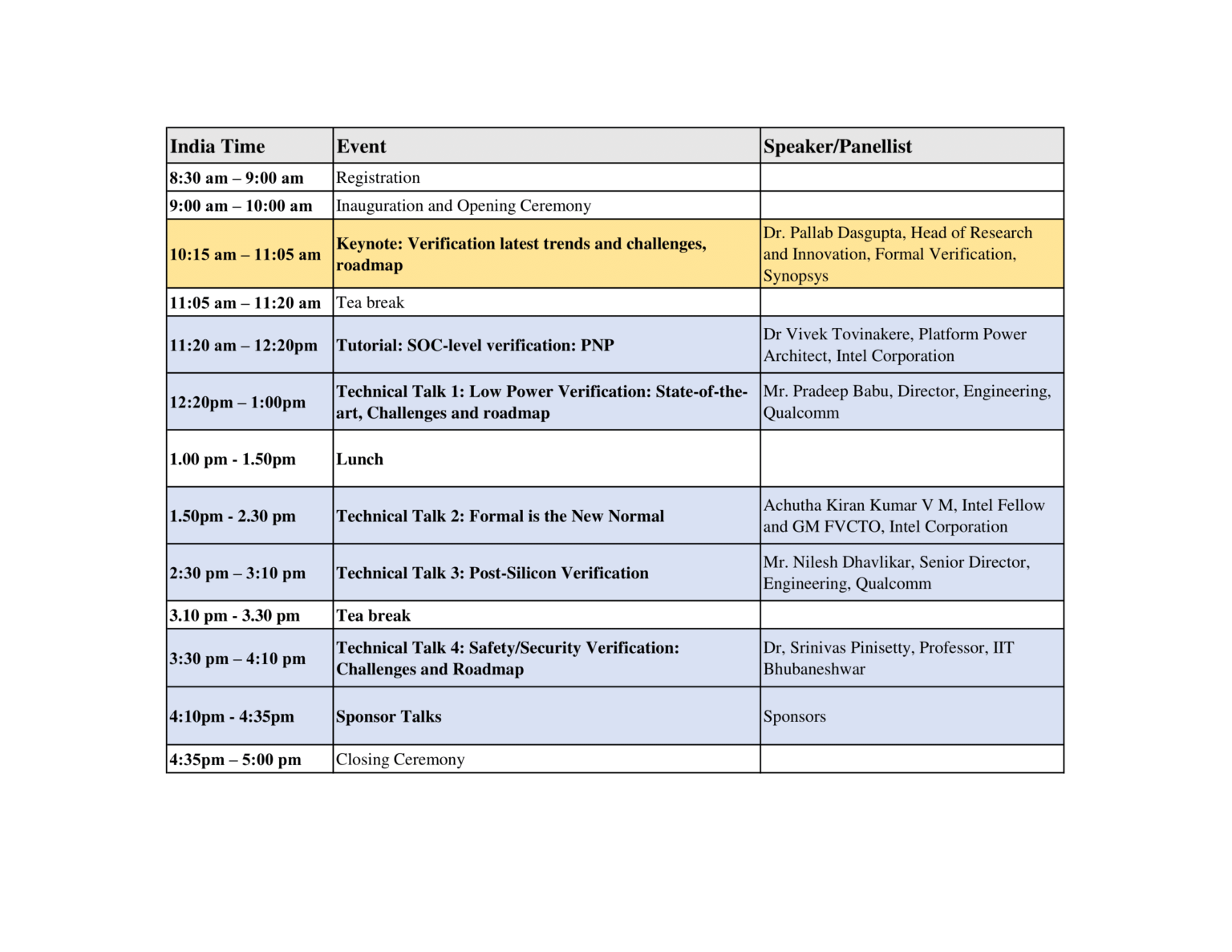

FULL DAY SCHEDULE

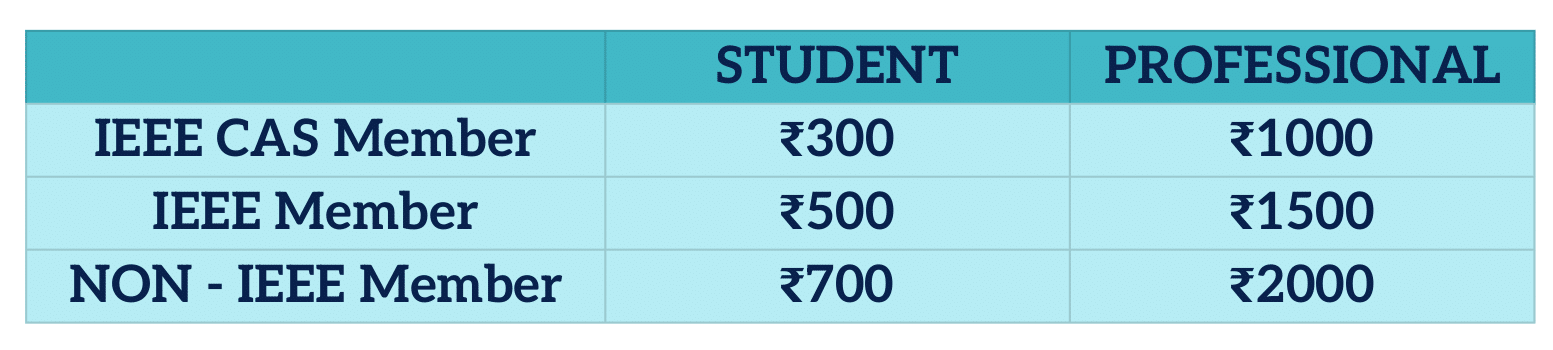

REGISTRATIONS

ORGANIZING COMMITTEE

Ayan Datta

Technologist Western Digital

Apurva Kumar

Quest Global, Director of Engineering

Sudipto Das

AVP Quest Global

Abhijeet Khopkar

Director R&D Synopsys

Dr. Sumantra Sarkar

MTS, AMD

Mr. Surinder Sood

ARM embedded technologies LTD, Principal Engineer

Kiran K R

Digital Design Engineer Intel

Dr. Srobona Mitra

Senior Staff Engineer/Mgr. Qualcomm

GUEST'S AND SPEAKER'S BRIEF

Dr. Chengappa M R

Dr. Chengappa has been associated with Hewlett Packard / Hewlett Packard Enterprise for the past decade. He is working as a Lead Engineer / Expert Technologist where he leads the customer consulting on end-to-end vRAN architecture with operators where he recommends apt architecture on end-to-end optimization of power consumption, security, and transport for Radio Access Network – RAN Infrastructure, Supporting RFx process with key lighthouse customers for infrastructure dimensioning and RAN site design for response. Leading the partner engagement Identifying and driving vRAN requirements into partner roadmap for new products. He has led the efforts to invent a new paradigm of distributed power and dormancy management for inline programmable environments (HPE / US patent pending). He is also contributing to the Working Groups in O-RAN Alliance and contributing to WG4, WG6, and also Telecom Infra Project.

Dr. Prasant Misra

Dr. Misra is the Chair of IEEE Computer Society Bangalore Chapter; Vice-Chair (Industry Engagements) of IEEE Bangalore Section; and an executive committee member of the COMSNETS Association. He is the Chair of the technical subcommittee for IoT, FutureSkills Prime (A MeitY – NASSCOM Digital Skilling Initiative) and is a member of the MeitY working group on IoT based technologies for Smart Cities. He has contributed to standardization initiatives on Smart Cities and Infrastructure for the Bureau of Indian Standards. He has served on the editorial board of IEEE Communications Magazine as Series Editor of Internet of Things (2019-2022); and is currently on the editorial boards of Elsevier Ad Hoc Networks Journal as Area Editor, and IEEE Intelligent Transportation Systems Magazine as Associate Editor.

Subind Kumar

Currently leading global product development team for Content Solution Group of Western Digital. The group is responsible for designing, developing, validating and volume production of removable products in SD/uSD, USB, CFast and Retail SSD. Experienced at leading Product Development teams both in Semiconductors (Networking and wireless) and Software (Networking and Wireless) spaces. Set technology directions, established new centers of excellence and strategic outsourcing partnerships. Successfully executed large projects (>$25M budgets). Deeply involved with M&A activities, marketing and business development initiatives. International experience in US, India, Singapore, France

Raj S Mitra

Dr Mitra received his Btech, Mtech and PhD degrees in Computer Science from IIT Kharagpur. He is a veteran in the EDA and verification industry, having worked at Cadence Synopsys and Interra Systems, and later served as Head of EDA at Texas

Instruments Bangalore. At TI, he had initiated several new methodologies, including formal verification and high level synthesis. Currently he is Director at Cisma Consultants, a subsidiary of Verikwest (USA), and drives projects related to formal verification, portable stimulus and machine learning there. He has published research papers in several IEEE

transactions journals and conferences, and has served in Technical Program Committees of DAC and VLSID conferences.

Dr. Pallab Dasgupta

Dr Pallab Dasgupta currently leads Research and Innovation on Formal Verification at Synopsys, Sunnyvale. He has more than 25 years of experience in formal verification technologies. He had been a professor and former Dean of Sponsored Research at the Indian Institute of Technology Kharagpur for many years, collaborating with many semiconductor and EDA companies, and heading one of the most well-known research groups on formal methods and EDA – one that has produced more than 250 research publications and generations of students who are formal verification practitioners today.

Mr. Achutha Kiran Kumar V M

Mr. Achutha Kiran Kumar V M is home grown Intel Fellow, joining as an RCG from IISc, Bangalore. He leads Formal Verification Central Tech Office (FVCTO) in the Product Enablement Solutions Group (PESG). He is recognized as an industry expert in FV and is responsible for defining and executing FV on IPs and SoCs from all Intel design organizations. In this role, Kiran strives to increase the formal footprint through various phases of the design cycle. He has co-authored a book titled Formal Verification – An Essential Toolkit to Hardware Designs, which is referenced in university courses. He has 1 patent, 100+ publications, and 15 best paper awards.

Mr. Nilesh Dhavlikar

Mr. Nilesh Dhavlikar has 20+ Years of Industry experience in VLSI Industry and and he has developed expertise in SOC Pre and Post Silicon validation. Currently he is leading & managing SVE (SOC validation & Emulation) team in Qualcomm for Snapdragon Mobile SOC chips driving overall SVE execution and enabling successful commercialization of chips used in mobile Handset, Compute, Automotive and Adjacent markets (IOT/XR). Nilesh has leadership experience in setting up large team with a mix of fresh and experienced SOC emulation & validation engineers and he is passionate about improving overall pre and post silicon validation methodology/flow and driving the debug of complex post Silicon issues. Nilesh holds Masters degree in Electrical Engineering from University of Nevada, USA.

Dr. Srinivas Pinisetty

Srinivas Pinisetty received a Ph.D. degree in Computer Science in January 2015 at INRIA, University of Rennes 1, Rennes, France. After completing master’s in Computer Science at Eindhoven University Technology (TU/e) in 2009, he continued as a PDEng trainee at TU/e for two years. For his master’s thesis project, he worked at ASML, Veldhoven, Netherlands in 2009, and as a Software Design Engineer trainee at Oc\’e Technologies, Venlo, Netherlands in 2011. He is an Assistant Professor in the School of Electrical Sciences at IIT Bhubaneswar. Prior to joining IIT Bhubaneswar he has worked as postdoctoral researcher at the University of Aalto, Finland, and later at the University of Gothenburg | Chalmers, Sweden. His research interests include formal methods, and software engineering in general, and runtime verification and enforcement in particular.

Dr. Vivek Tovinakere

Dr. Vivek Tovinakere is currently a FPGA Platform Power Architect in the Programmable Solutions Group of Intel. He has been with Intel for 8 years working on modeling, estimation and optimization of Power and Performance of Client SoCs, High Performance Computing and FPGA products. He has about 22 years of experience in various roles working in different companies of the semiconductor industry including about 4 years as a researcher in a national research laboratory. He holds a PhD from University of Rennes 1, France, a Master’s degree in EE from IIT-Kanpur and a Bachelor’s degree in ECE from University of Mysore respectively. He is a Senior Member of the IEEE as well as a member of CAS society.

Mr. Pradeep Babu

Pradeep Babu has 24 years of experience in SOC Design Verification and Validation. Expert in Automotive Functional Safety Verification and Lead multiple ASIL-D/B SOCs in Qualcomm. Established Safety verification flow and process across Qualcomm IPs and SOCs development. Engaged in Automotive Customer audits and ISO26262 Compliance process, audits and certification. Experienced in SOC Power and System Verification. Delivered successful products across multiple application space in the industry – NFC, UWB, Automotive Infotainment, ADAS and High-end Security DVR markets. Pradeep Babu received Bachelor’s degree from Madras University. Published multiple papers and holding 2 US Patents. Actively contribute to Verification community (Multiple times Judge in CDN Live, DVCON2022 Panel discussion and provided key-note on Advance Formal club event 2018)

SPONSORS